# MG87FE/L2051/4051/6051 Data Sheet

Ver 1.03

This document information is the intellectual property of Megawin Technology.  $\circledcirc$  Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D

### Content

| 1.      | General Description                                                        | 4    |

|---------|----------------------------------------------------------------------------|------|

| 2.      | Features                                                                   | 5    |

| 3.      | Block Diagram                                                              | 6    |

| 4.      | Pin Configurations                                                         |      |

|         | 4.1. Package Instruction                                                   |      |

|         | 4.2. Pin Description (PDIP-20 & SOP-20)                                    |      |

| 5.      | 8051 CPU Function Description                                              | 9    |

|         | 5.1. CPU Register                                                          |      |

|         | 5.2. CPU Timing                                                            | . 10 |

|         | 5.3. CPU Addressing Mode                                                   | . 10 |

| 6.      | Memory Organization                                                        | 11   |

|         | 6.1. On-Chip Program Flash                                                 |      |

|         | 6.2. On-Chip Data RAM                                                      |      |

| 7.      | Special Function Register                                                  | 13   |

|         | 7.1. SFR Map                                                               |      |

|         | 7.2. SFR Bit Assignment                                                    |      |

| 8.      | Configurable I/O Ports                                                     | 16   |

|         | 8.1. IO Structure                                                          |      |

|         | 8.1.1. Port1/3/4 GPIO Structure                                            |      |

|         | 8.2. Port1 Register                                                        |      |

|         | 8.3. Port3 Register                                                        |      |

| 0       | 8.4. Port4 Register                                                        |      |

| 9.      | Interrupt.                                                                 |      |

|         | <ul><li>9.1. Interrupt Structure</li><li>9.2. Interrupt Register</li></ul> |      |

| 10      | Timers/Counters                                                            |      |

| 10.     | 10.1. Timer0 and Timer1                                                    |      |

|         | 10.1.1. Mode 0 Structure                                                   |      |

|         | 10.1.2. Mode 1 Structure                                                   |      |

|         | 10.1.3. Mode 2 Structure                                                   |      |

|         | 10.1.4. Mode 3 Structure                                                   |      |

|         | 10.1.5. Timer0/1 Register                                                  |      |

|         | 10.2. PWM-Timer                                                            | . 27 |

|         | 10.2.1. PWM-Timer Structure                                                |      |

|         | 10.2.2. PWM-Timer Register                                                 |      |

| 11.     | UART                                                                       |      |

|         | 11.1. UART Structure                                                       |      |

|         | 11.2. UART Register                                                        |      |

| 12.     | Analog Comparator                                                          |      |

|         | 12.1. Analog Comparator Structure                                          |      |

|         | 12.2. Analog Comparator Register                                           |      |

| 13.     | Watch Dog Timer (WDT)                                                      |      |

|         | 13.1. WDT Structure                                                        |      |

|         | 13.2. WDT Register                                                         | . 35 |

| This do | ocument information is the intellectual property of Megawin Technology.    |      |

<sup>©</sup> Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D

### MG87FE/L2051/4051/6051

Preliminary Ver 1.00

| 14. | Reset                                         |    |

|-----|-----------------------------------------------|----|

|     | 14.1. Reset Source                            |    |

| 15. | Power Management                              |    |

|     | 15.1. Power Saving Mode                       |    |

|     | 15.1.1. Idle Mode                             |    |

|     | 15.1.2. Power-down Mode                       |    |

|     | 15.1.3. Interrupt Recovery from Power-down    |    |

|     | 15.1.4. Reset Recovery from Power-down        |    |

|     | 15.1.5. GPIO wake-up Recovery from Power-down |    |

|     | 15.2. Power Control Register                  |    |

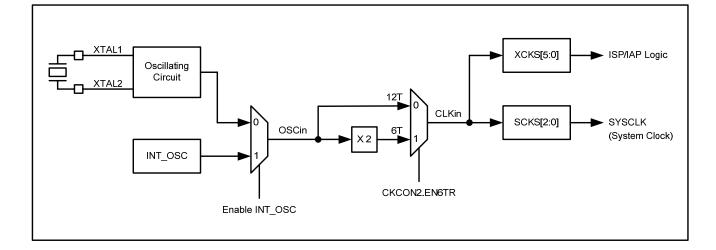

| 16. | System Clock                                  | 41 |

|     | 16.1. Clock Structure                         |    |

|     | 16.2. Clock Register                          |    |

| 17. | In System Programming (ISP)                   | 43 |

| 18. | In Application Programming (IAP)              | 45 |

| 19. | Auxiliary SFRs                                |    |

| 20. | Option Setting                                |    |

| 21. | Absolute Maximum Rating                       |    |

| 22. | Electrical Characteristics                    | 50 |

|     | 22.1. DC Characteristics                      | 50 |

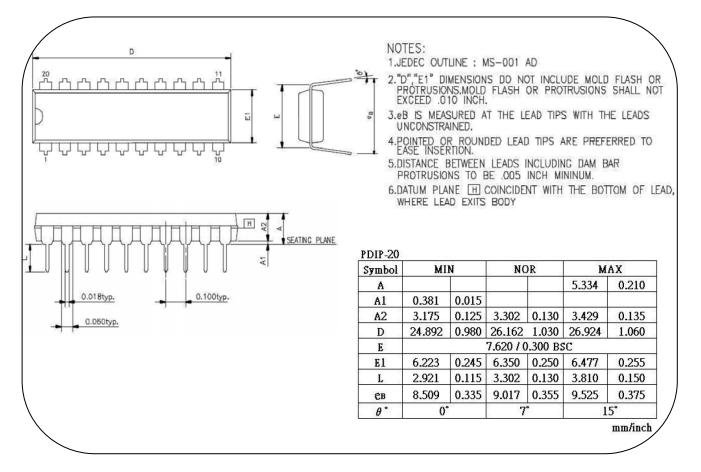

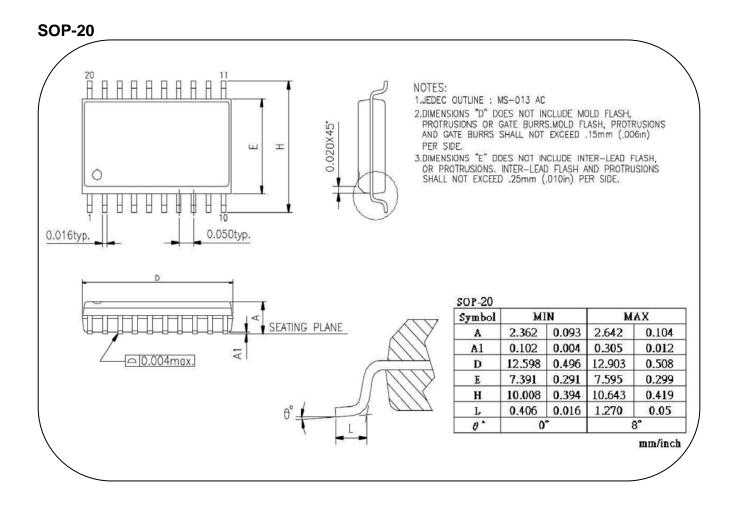

| 23. | Package Dimension                             | 51 |

| 24. | Instruction Set                               |    |

| 25. | Revision History                              |    |

# **1. General Description**

MG87FE/L2051/4051/6051 is single-chip 8-bits microcontroller with the instruction sets fully compatible with industrial-standard 80C51 series microcontroller. 2K/4K/6K bytes flash memory and 256 bytes RAM has been embedded to provide widely field application. In-System-Programming and In-Application-Programming allows the users to download new code or data while the microcontroller sits in the application. This device executes one machine cycle in 6 clock cycles or 12 clock cycles. MG87FE/L2051/4051/6051 has one 8-bit I/O ports (P1), one 7-bit I/O port (P30~P35,P37), two 16-bit timer/counters, one PWM-timer for 8-channel PWM output, a seven -source, four-priority-level interrupt structure, an enhanced UART, a precision analog comparator, on-chip crystal oscillator(combined P42,P43) and a high-precision internal oscillator.

### MG87FE/L2051/4051/6051

# 2. Features

- 80C51 Central Processing Unit

- MG87FE/L2051 with 2KB flash ROM, 4051/4KB flash ROM; 6051/6KB flash ROM

- Operating voltage: E type: 4.5V~5.5V and L type: 2.4V~3.6V

- Operation frequency : 48MHz(max)@12T and 24MHz@6T mode

- External crystal mode

- Internal RC-oscillator with +/- 4% frequency drift @ -40 ~ 85°C, there are 6 kinds of frequencies selectable:

|   | Internal oscillator frequency |

|---|-------------------------------|

| 1 | 6MHz                          |

| 2 | 11.059MHz                     |

| 3 | 12MHz                         |

| 4 | 22.118MHz                     |

| 5 | 24MHz                         |

| 6 | 24.576MHz                     |

- ISP memory zone could be optioned as 0.5K/1KB/1.5KB~3.5KB

- IAP capability; 1KB IAP memory size

- On-chip 256 bytes data RAM for MG87FE/L2051/4051/6051

- Code protection for flash memory access

- Two 16-bit timer/counter

- PWM-Timer for PWM generator or normal 8-bit timer, selectable interrupt on INT3

- Seven sources, four-level-priority interrupt capability.

- Enhanced UART, provides frame-error detection and hardware address-recognition

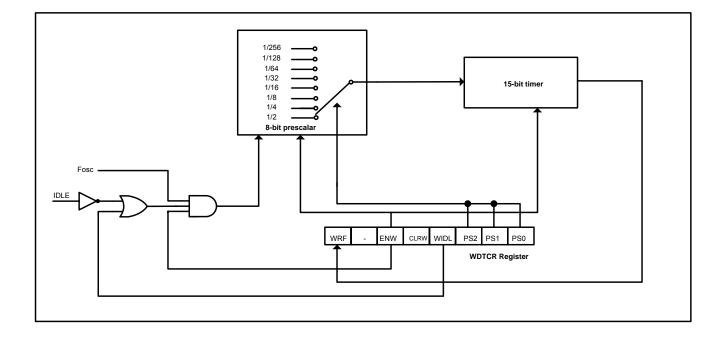

- 15 bits Watch-Dog-Timer with 8-bit pre-scalar, one-time enabled by CPU or power-on

- Power control: idle mode and power-down mode, Power-down can be woken-up by INT0(P3.2), INT1(P3.3), INT2(P4.3), INT3(P4.2) and other I/O.

- I/O port list, P1[7:0], P3[7,5:0], P4.2/INT3 on XTAL2, P4.3/INT2 on XTAL1

- Built-in analog comparator with selectable interrupt on INT2. AIN0(V+) on P1.0 and AIN1(V-) on P1.1, output on P3.6

- Package type: PDIP-20, SOP-20

| Items          | Package Type | Description                  |

|----------------|--------------|------------------------------|

| MG87Fxy051AE20 | PDIP-20      | x = E:5.0V , L:3.3V          |

| MG87Fxy051AS20 | SOP-20       | y = 2, 4, 6 . 2051/4051/6051 |

This document information is the intellectual property of Megawin Technology.  $\circledcirc$  Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D

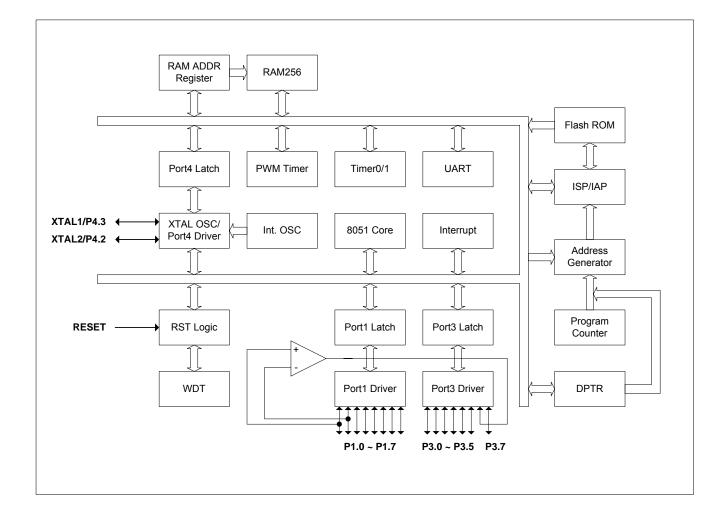

# 3. Block Diagram

MG87FE/L2051/4051/6051

Preliminary Ver 1.00

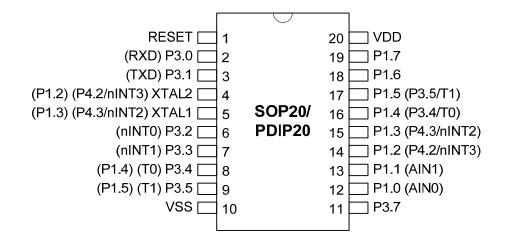

# 4. Pin Configurations

# 4.1. Package Instruction

This document information is the intellectual property of Megawin Technology. © Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D

# 4.2. Pin Description (PDIP-20 & SOP-20)

| Pin Name   | Pin Number | I/O type | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.0~P1.7  | 12~19      | I/O      | <b>Port1</b> : General-purposed I/O with weak pull-up resistance inside.<br>When 1s are written into Port1, the strong output driving PMOS<br>only turn-on two periods and then the weak pull-up resistance<br>keeps the port high.<br>P1.0 is the comparator positive input.                                                                                                                  |

|            |            |          | <ul> <li>P1.1 is the comparator negative input.</li> <li>P1.2 has a swapped function with P4.2/INT3.</li> <li>P1.3 has a swapped function with P4.3/INT2.</li> <li>P1.4 has a swapped function with P3.4/T0.</li> <li>P1.5 has a swapped function with P3.5/T1.</li> </ul>                                                                                                                     |

| P3.0~P3.7  | 2~3,6~9,11 | I/O      | <b>Port3</b> : General-purposed I/O with weak pull-up resistance inside.<br>When 1s are written into Port1, the strong output driving PMOS<br>only turn-on two periods and then the weak pull-up resistance to<br>keep the port high. Port3 also serves the special function of<br>MG87FE/L2051/4051/6051.<br>P3.4 has a swapped function with P1.4.<br>P3.5 has a swapped function with P1.5. |

| RESET      | 1          | I        | <b>RESET</b> : A high on this pin for at least two machine cycles will reset the device.                                                                                                                                                                                                                                                                                                       |

| XTAL1/P4.3 | 5          | I/O      | <b>Crystal1</b> : Input to the inverting oscillator amplifier.<br>XTAL1 has an alternate function for P4.3/INT2.                                                                                                                                                                                                                                                                               |

|            |            |          | P4.3/INT2 has a swapped function with P1.3.                                                                                                                                                                                                                                                                                                                                                    |

| XTAL2/P4.2 | 4          | I/O      | Crystal2: Output from the inverting amplifier.                                                                                                                                                                                                                                                                                                                                                 |

|            |            |          | XTAL2 has an alternate function for P42/INT3.<br>P4.2/INT3 has a swapped function with P1.2.                                                                                                                                                                                                                                                                                                   |

| VDD        | 20         | Р        | POWER                                                                                                                                                                                                                                                                                                                                                                                          |

| VSS        | 10         | G        | GROUND                                                                                                                                                                                                                                                                                                                                                                                         |

# 5. 8051 CPU Function Description

# 5.1. CPU Register

#### **PSW: Program Status Word**

Address=D0H, read/write, Power On + RESET=0000-0000

| 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |  |  |  |

|----|----|----|-----|-----|----|----|---|--|--|--|

| CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |  |  |  |

CY: Carry bit.

AC: Auxiliary carry bit. F0: General purpose flag 0. RS1: Register bank select bit 1. RS0: Register bank select bit 0. OV: Overflow flag. F1: General purpose flag 1. P: Parity bit.

The program status word(PSW) contains several status bits that reflect the current state of the CPU. The PSW, shown above, resides in the SFR space. It contains the Carry bit, the Auxiliary Carry(for BCD operation), the two register bank select bits, the Overflow flag, a Parity bit and two user-definable status flags.

The Carry bit, other than serving the function of a Carry bit in arithmetic operations, also serves as the "Accumulator" for a number of Boolean operations.

The bits RS0 and RS1 are used to select one of the four register banks shown in the on-chip-data-RAM section. A number of instructions refer to these RAM locations as R0 through R7.

The Parity bit reflects the number of 1s in the Accumulator. P=1 if the Accumulator contains an odd number of 1s and otherwise P=0.

#### SP: Stack Pointer

Address=81H, read/write, Power On + RESET=0000-0111

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|

| SP[7] | SP[6] | SP[5] | SP[4] | SP[3] | SP[2] | SP[1] | SP[0] |  |

#### DPL: Data Pointer Low

Address=82H, read/write, Power On + RESET=0000-0000

| 7      | 6      | 5 4    |        | 3      | 2      | 1      | 0      |  |

|--------|--------|--------|--------|--------|--------|--------|--------|--|

| DPL[7] | DPL[6] | DPL[5] | DPL[4] | DPL[3] | DPL[2] | DPL[1] | DPL[0] |  |

#### DPH: Data Pointer High

Address=83H, read/write, Power On + RESET=0000-0000

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| DPH[7] | DPH[6] | DPH[5] | DPH[4] | DPH[3] | DPH[2] | DPH[1] | DPH[0] |

#### **B: B Register**

Address=F0H, read/write, Power On + RESET=0000-0000

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| B[7] | B[6] | B[5] | B[4] | B[3] | B[2] | B[1] | B[0] |

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

# 5.2. CPU Timing

A machine cycle is the shortest timing period to achieve an instruction. In MG87FE/L2051/4051/6051, some instructions need 1 machine cycle to achieve, but others need 2 or 4 machine cycles. A machine cycle takes 12 clock periods or 6 clock periods. For 12MHz system clock, it is 1us or 0.5us.

A machine cycle is consisted of six sequential states. The states are from S1 to S6. For each state, it is partitioned into two phase – phase1 and phase2. Each phase is corresponding to 1 clock period. Execution of a one-cycle instruction begins during S1 when the op-code is latched into the instruction register. A second fetch appears during S4 of the same machine cycle. Execution is completed at the end of S6 of the machine cycle.

MOVX instruction is in-active in MG87FE/L2051/4051/6051 because there is no on-chip external RAM and no external access bus. Write operation will have no effect. And read operation will always cause an un-excepted operation.

# 5.3. CPU Addressing Mode

#### Direct Addressing (DIR)

In direct addressing the operand is specified by an 8-bit address field in the instruction. Only internal data RAM and SFRs can be direct addressed.

#### Indirect Addressing (IND)

In indirect addressing the instruction specified a register which contains the address of the operand. Both internal and external RAM can be indirectly addressed.

The address register for 8-bit addresses can be R0 or R1 of the selected bank, or the Stack Pointer. The address register for 16-bit addresses can only be the 16-bit data pointer register – DPTR.

#### **Register Instruction (REG)**

The register banks, containing registers R0 through R7, can be accessed by certain instructions which carry a 3-bit register specification within the op-code of the instruction. Instructions that access the registers this way are code efficient because this mode eliminates the need of an extra address byte. When such instruction is executed, one of the eight registers in the selected bank is accessed.

#### **Register-Specific Instruction**

Some instructions are specific to a certain register. For example, some instructions always operate on the accumulator or data pointer, etc. No address byte is needed for such instructions. The op-code itself does it.

#### Immediate Constant (IMM)

The value of a constant can follow the op-code in the program memory.

#### Index Addressing

Only program memory can be accessed with indexed addressing and it can only be read. This addressing mode is intended for reading look-up tables in program memory. A 16-bit base register(either DPTR or PC) points to the base of the table, and the accumulator is set up with the table entry number. Another type of indexed addressing is used in the conditional jump instruction.

In conditional jump, the destination address is computed as the sum of the base pointer and the accumulator.

This document information is the intellectual property of Megawin Technology.

<sup>©</sup> Megawin Technology Co., Ltd. 2009 All rights reserved.

# 6. Memory Organization

MG87FE/L2051/4051/6051 device has separate address spaces for program and data memory. On-chip data memory can be accessed by 8-bit addresses, which can be quickly stored and manipulated by the 8-bit CPU. Program memory in MG87FE/L2051/4051/6051 can only be read, not written into.

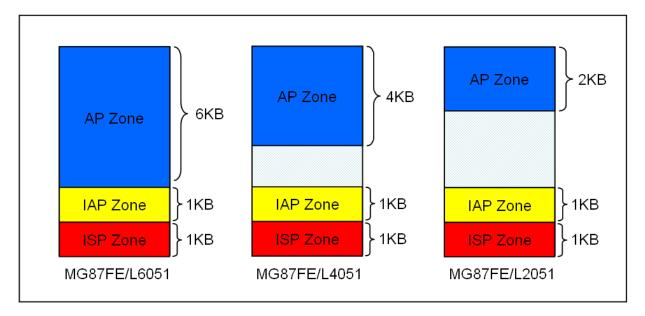

# 6.1. On-Chip Program Flash

In MG87FE/L2051/4051/6051, the first partition named AP-memory is the space for storing user's application program code. The second one named as IAP-memory and the space which is accessed by CPU for storing the user data. The third is named as ISP-memory and it is special for ISP boot code program.

# 6.2. On-Chip Data RAM

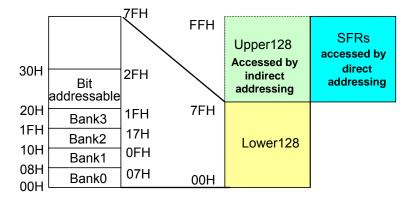

MG87FE/L2051/4051/6051 has internal data RAM that is mapped into three separate segments. They are lower 128 bytes of RAM, upper 128 bytes of RAM and 128 bytes Special Function Register (SFR).

- 6.2.1 Lower 128 bytes of RAM: (addresses 0x00 to 0x7F) are accessed by either direct or indirect addressing.

- 6.2.2 Upper 128 bytes of RAM: (addresses 0x80 to 0xFF) are accessed only by indirect addressing (using R0 or R1).

- 6.2.3 The Special Function Registers: (addresses 0x80 to 0xFF) are accessed only by direct addressing.

# 7. Special Function Register

# 7.1.SFR Map

|     | 0/8               | 1/9               | 2/A                | 3/B                | 4/C                | 5/D              | 6/E                | 7/F                |     |

|-----|-------------------|-------------------|--------------------|--------------------|--------------------|------------------|--------------------|--------------------|-----|

| F8H |                   |                   | CCAP0H<br>00000000 |                    |                    |                  |                    |                    | FFH |

| F0H | B<br>00000000     |                   |                    |                    |                    |                  |                    |                    | F7H |

| E8H | P4<br>XXXX11XX    |                   | CCAP0L<br>00000000 |                    |                    |                  |                    |                    | EFH |

| E0H |                   | WDTCR<br>0X000000 | IFD<br>11111111    | IFADRH<br>00000000 | IFADRL<br>00000000 | IFMT<br>XXXX0000 | SCMD<br>XXXXXXXX   | ISPCR<br>0000XXXX  | E7H |

| D8H | CCON<br>00XXXXXX  | CMOD<br>00000000  |                    |                    |                    |                  |                    |                    | DFH |

| D0H | PSW<br>00000000   |                   |                    |                    |                    |                  | P3WKPE<br>0X000000 | P1WKPE<br>00000000 | D7H |

| C8H |                   |                   |                    |                    |                    |                  |                    |                    | CFH |

| Сон | XICON<br>00000000 |                   |                    |                    |                    |                  |                    | CKCON<br>XXXXX000  | С7Н |

| B8H | IPL<br>XXX00000   | SADEN<br>00000000 |                    |                    |                    |                  |                    | CKCON2<br>XX001010 | BFH |

| B0H | P3<br>11111111    |                   |                    |                    |                    |                  |                    | IPH<br>00X00000    | B7H |

| A8H | IE<br>0XX00000    | SADDR<br>00000000 |                    |                    |                    |                  |                    |                    | AFH |

| A0H |                   |                   | AUXR1<br>0XXX0XXX  |                    |                    |                  |                    |                    | A7H |

| 98H | SCON<br>00000000  | SBUF<br>XXXXXXXX  |                    |                    |                    |                  |                    |                    | 9FH |

| 90H | P1<br>11111111    |                   |                    | TSTWD<br>0X000000  |                    |                  |                    | ACSR<br>0XX00000   | 97H |

| 88H | TCON<br>00000000  | TMOD<br>00000000  | TL0<br>00000000    | TL1<br>00000000    | TH0<br>00000000    | TH1<br>00000000  | AUXR<br>00000000   | CKCON3<br>XXXXXX0X | 8FH |

| 80H |                   | SP<br>00000111    | DPL<br>00000000    | DPH<br>00000000    |                    |                  |                    | PCON<br>00010000   | 87H |

|     | 0/8               | 1/9               | 2/A                | 3/B                | 4/C                | 5/D              | 6/E                | 7/F                |     |

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 13/56

# 7.2. SFR Bit Assignment

| SYMBOL | DESCRIPTION            | ADDRESS |             | E     | BIT AD      | DRESS       | AND   | SYMBO       | DL          |            | INITIAL                |

|--------|------------------------|---------|-------------|-------|-------------|-------------|-------|-------------|-------------|------------|------------------------|

|        |                        |         |             |       |             |             |       |             |             | LSB        |                        |

| SP     | Stack Pointer          | 81H     |             |       |             |             |       |             |             |            | 00000111B              |

| DPL    | Data Pointer Low       | 82H     |             |       |             |             |       |             |             |            | 0000000B               |

| DPH    | Data Pointer High      | 83H     |             | -     |             | -           |       |             | -           |            | 0000000B               |

| PCON   | Power Control          | 87H     | SMOD        |       | PWMEN       | POF         | GF1   | GF0         | PD          | IDL        | 00010000B              |

| TCON   | Timer Control          | 88H     | 9FH         | 9EH   | 9DH         | 9CH         | 9BH   | 9AH         | 89H         | 88H        | 0000000B               |

|        |                        |         | TF1         | TR1   | TF0         | TR0         | IE1   | IT1         | IE0         | IT0        |                        |

| TMOD   | Timer Mode             | 89H     | GATE        | C/T   | M1          | MO          | GATE  | C/T         | M1          | M0         | 0000000B               |

| TL0    | Timer Low 0            | 8AH     |             |       |             |             |       |             |             |            | 0000000B               |

| TL1    | Timer Low 1            | 8BH     |             |       |             |             |       |             |             |            | 0000000B               |

| TH0    | Timer High 0           | 8CH     |             |       |             |             |       |             |             |            | 0000000B               |

| TH1    | Timer High 1           | 8DH     |             |       |             |             | -     |             |             |            | 0000000B               |

| AUXR   | Auxiliary              | 8EH     | INT3H       | INT2H | P15FS       | P14FS       | P13FS | P12FS       | P11PU       | P10PU      | 0000000B               |

| CKCON3 | Clock Control 3        | 8FH     | -           | -     | -           | -           | -     | -           | PWDEX       |            | xxxxxx0xB              |

| P1     | Port 1                 | 90H     | 97H         | 96H   | 95H         | 94H         | 93H   | 92H         | 91H         | 90H        | 11111111B              |

| ACSR   | Analog Comp. Reg.      | 97H     | ACIDX       | -     | -           | ACF         | ACEN  | ACM2        | ACM1        | ACM0       | 0xx00000B              |

| SCON   | Serial Control         | 98H     | 9FH         | 9EH   | 9DH         | 9CH         | 9BH   | 9AH         | 99H         | 98H        | 0000000B               |

|        |                        |         | SM0         | SM1   | SM2         | REN         | TB8   | RB8         | TI          | RI         |                        |

| SBUF   | Serial Buffer          | 99H     | /FE         |       |             |             |       |             |             |            | Nagagaga (D            |

| AUXR1  | Auxiliary 1            | A2H     | P14FD       |       |             |             | GF2   |             |             |            | xxxxxxxB<br>0xxx0xxxB  |

|        | ,,                     |         | AFH         | AEH   | -<br>ADH    | ACH         | ABH   | -<br>AAH    | -<br>A9H    | -<br>A8H   |                        |

| IE     | Interrupt Enable       | A8H     | EA          | EAC   | ADH         | ES          | ET1   | EX1         | ET0         | EX0        | 0xx00000B              |

| SADDR  | Slave Address          | A9H     |             | LAC   |             | LU          |       | LAI         | LIU         | LXU        | 00000000B              |

| P3     | Port 3                 | BOH     | B7H         | B6H   | B5H         | B4H         | B3H   | B2H         | B1H         | B0H        | 1x111111B              |

| P3     | 1011 3                 | БОП     | 5/11        | DOLL  | T1          | T0          | INT1  | INT0        | TXD         | RXD        | IXIIIIID               |

| IPH    | Interrupt Priority     | B7H     | PX3H/       | PX2H/ |             | PSH         | PT1H  | PX1H        | PTOH        | PX0H       | 00x00000B              |

|        | High                   | 0/11    | PTCH        | PACH  |             | 1 011       |       | 1 / 11      | 1 1011      | 1 //011    | 00000000               |

| IPL    | Interrupt Priority Low | B8H     | BFH         | BEH   | BDH         | BCH         | BBH   | BAH         | B9H         | B8H        | xxx00000B              |

| –      |                        | 2011    |             | PAC   |             | PS          | PT1   | PX1         | PT0         | PX0        |                        |

| SADEN  | Slave Address Mask     | B9H     |             |       |             |             |       |             |             |            | 00000000B              |

| CKCON2 | Clock Control 2        | BFH     | OSCDR       | EN6TR | XCKS5       | XCKS4       | XCKS3 | XCKS2       | XCKS1       | XCKS0      | xx001010B              |

| XICON  | Ext. Interrupt Control | C0H     | C7H         | C6H   | C5H         | C4H         | C3H   | C2H         | C1H         | C0H        | 0000000B               |

|        |                        |         | PX3/        | EX3   | IE3         | IT3         | PX2   | EX2         | IE2         | IT2        |                        |

|        |                        |         | PTC         |       |             |             |       |             |             |            |                        |

| CKCON  | Clock Control          | C7H     | -           | -     | -           | -           | -     | SCKS2       | SCKS1       |            | xxxxx000B              |

| PSW    | Program Status         | D0H     | D7H         | D6H   | D5H         | D4H         | D3H   | D2H         | D1H         | D0H        | 0000000B               |

|        | Word                   |         | CV/         | 40    | 50          | D01         | DCO   | OV          |             | Р          |                        |

|        |                        | DOLL    |             | AC    | F0          | RS1         | RS0   | -           |             |            | 0x000000B              |

| P3WKPE | P3 Wake-up Enable      | D6H     | P37WE       |       |             |             |       |             |             |            |                        |

| P1WKPE | P1 Wake-up Enable      | D7H     |             |       | P15WE       | P14WE       | P13WE | P12WE       | PTIWE       | PIOWE      | 0000000B               |

| CCON   | Counter Control        | D8H     | CF          | CR    | -           | -           | -     | -           | -           | -          | 00xxxxxB               |

| CMOD   | Reg.                   |         |             | POS2  | DOG1        | DOSO        | CPS2  | CDC1        | CDCO        | ECE        | 00000000               |

|        | Counter Mode Reg.      | D9H     | CIDL<br>WRF |       | POS1<br>ENW | POS0<br>CLW | WIDL  | CPS1<br>PS2 | CPS0<br>PS1 | ECF<br>PS0 | 00000000B              |

| WDTCR  | Watch-dog-timer        | E1H     |             | -     |             | CLVV        | VVIDL | F32         | F31         | F30        | 0x000000B              |

|        | Control register       |         |             | l     |             | l           |       |             | l           |            | 111111111              |

| IFD    | ISP Flash data         | E2H     |             |       |             |             |       |             |             |            | 11111111B              |

| IFADRH | ISP Flash address      | E3H     |             |       |             |             |       |             |             |            | 00000000B              |

|        | High                   |         |             |       |             |             |       |             |             |            | 000000000              |

| IFADRL | ISP Flash Address      | E4H     |             |       |             |             |       |             |             |            | 00000000B              |

| IFMT   | Low<br>ISP Mode Table  | E5H     |             |       |             | -           | MS3   | MS2         | MS1         | MS0        |                        |

| IAPLB  | IAP Low Boundary       |         | -           |       | -           |             | 10133 | IVI32       | NIG I       | 10130      | xxxx0000B<br>11111111B |

|        | IAP LOW BOUIDARY       | Note 1  |             |       |             |             |       |             |             |            | IIIIID                 |

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 14/56

### MG87FE/L2051/4051/6051

Preliminary Ver 1.00

|        | ISP Serial Command   | E6H |       |     |      |       |     |     |     |     | xxxxxxB   |

|--------|----------------------|-----|-------|-----|------|-------|-----|-----|-----|-----|-----------|

| ISPCR  | ISP Control Register | E7H | ISPEN | BS  | SRST | CFAIL | -   | -   | -   | -   | 0000xxxxB |

| P4     | Port 4               | E8H | -     | -   | -    | -     | EBH | EAH |     |     | xxxx11xxB |

| CCAP0L |                      | EAH |       |     |      |       |     |     |     |     | 0000000B  |

| В      | B Register           | F0H | F7H   | F6H | F5H  | F4H   | F3H | F2H | F1H | F0H | 0000000B  |

| CCAP0H |                      | FAH |       |     |      |       |     |     |     |     | 0000000B  |

Note1: The registers are addressed by IFMT and SCMD. Please refer the IFMT register description for more detail information.

# 8. Configurable I/O Ports

### 8.1.IO Structure

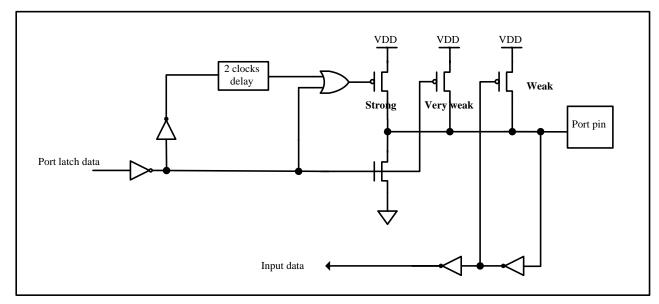

### 8.1.1.Port1/3/4 GPIO Structure

By the way, the pull-up resistor is disabled on P10/P11 in default.

# 8.2. Port1 Register

#### P1: Port 1 Register

| Address=90 | H, read/write | , Power On + | RESET=11 | 11-1111 |     |     |     |

|------------|---------------|--------------|----------|---------|-----|-----|-----|

| 7          | 6             | 5            | 4        | 3       | 2   | 1   | 0   |

| P17        | P16           | P15          | P14      | P13     | P12 | P11 | P10 |

Bit 7~0: P17~P10 could be set/cleared by CPU. Or it also can be toggled on addressed port channel by PWM-Timer underflow event in PWM mode.

# 8.3. Port3 Register

#### P3: Port 3 Register

Address=B0H, read/write, Power On + RESET=1X11-1111

| / laal 000 D0 |     |     |     |     |     |     |     |  |

|---------------|-----|-----|-----|-----|-----|-----|-----|--|

| 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

| P37           | P36 | P35 | P34 | P33 | P32 | P31 | P30 |  |

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 16/56

Bit 7, 5~0: P37, P35~P30 could only be set/cleared by CPU. P36 is read only for CPU from analog comparator output.

# 8.4. Port4 Register

#### P4: Port 4 Register

Address=E8H, read/write, Power On + RESET=XXXX-11XX

| Addiess-Ec |   |   |   |     |     |   |   |  |

|------------|---|---|---|-----|-----|---|---|--|

| 7          | 6 | 5 | 4 | 3   | 2   | 1 | 0 |  |

| -          | - | - | - | P43 | P42 | - | - |  |

Bit 3~2: P43~P42 could be only be set/cleared by CPU.

# 9. Interrupt

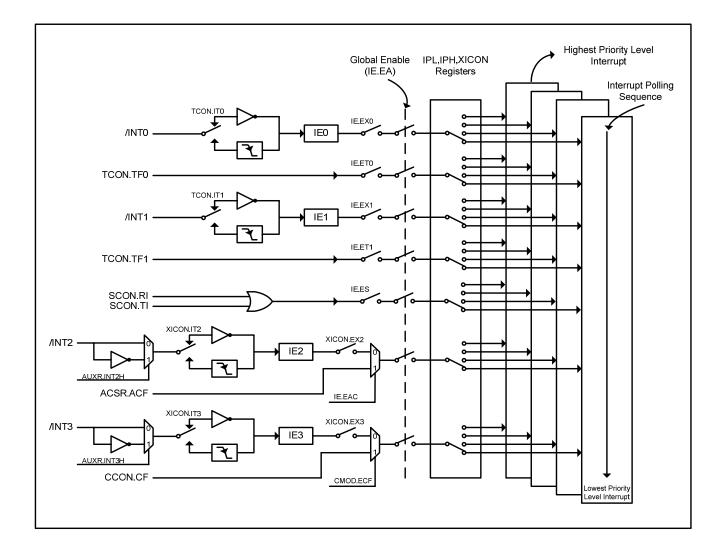

# 9.1. Interrupt Structure

# 9.2. Interrupt Register

#### IE: Interrupt Enable Register

Address=E8H, read/write, Power On + RESET=00X0-0000

| 7  | 6   | 5 | 4  | 3   | 2   | 1   | 0   |  |

|----|-----|---|----|-----|-----|-----|-----|--|

| EA | EAC |   | ES | ET1 | EX1 | ET0 | EX0 |  |

Bit 7: EA, All interrupts enable register.

0: Global disables all interrupts.

1: Global enables all interrupts.

Bit 6: EAC, Analog Comparator interrupt Enable register.

0: Disable analog comparator interrupt and reserve the interrupt vector (33H) to /INT2.

1: Enable analog comparator interrupt and occupy the /INT2 interrupt vector (33H) for analog comparator event. In this mode, IE2 still maintains its original function but it will not generate an interrupt whether EX2 is set or not.

Bit 5: Reserved.

Bit 4: ES, Serial port interrupt enable register.

- 0: Disable serial port interrupt.

- 1: Enable serial port interrupt.

Bit 3: ET1, Timer 1 interrupt enable register.

- 0: Disable Timer 1 interrupt.

- 1: Enable Timer 1 interrupt.

Bit 2: EX1, External interrupt 1 enable register.

- 0: Disable external interrupt 1.

- 1: Enable external interrupt 1.

Bit 1: ET0, Timer 0 interrupt enable register.

- 0: Disable Timer 0 interrupt.

- 1: Enable Timer 1 interrupt.

Bit 0: EX0, External interrupt 0 enable register.

- 0: Disable external interrupt 0.

- 1: Enable external interrupt 1.

#### XICON: External Interrupt Control Register

Address=C0H, read/write, Power On + RESET=0000-0000

| 7.0000000 |     |     |     |     |     |     |     |  |

|-----------|-----|-----|-----|-----|-----|-----|-----|--|

| 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

| PX3/PTC   | EX3 | IE3 | IT3 | PX2 | EX2 | IE2 | IT2 |  |

Bit 7: PX3, External interrupt 3 priority-L register.

0: Lower priority, setting with PX3H to select priority level.

1: Higher priority, setting with PX3H to select priority level.

Bit 7: PTC, PWM-Timer interrupt priority-L register. PX3 has an alternated function, PTC, that is switched by ECF. When ECF is set, this bit is PTC function. If cleared, this bit is PX3 function.

0: Lower priority, setting with PTCH to select priority level.

This document information is the intellectual property of Megawin Technology.

Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D

1: Higher priority, setting with PTCH to select priority level.

Bit 6: EX3, external interrupt 3 enable register.

- 0: Disable external /INT3.

- 1: Enable external /INT3. This function will be masked when CMOD.ECF is enabled.

- Bit 5: IE3, Interrupt 3 Edge flag.

- 0: Cleared when interrupt start to be serviced. It also could be cleared by CPU.

- 1: Set by hardware when external interrupt edge detected. It also could be set by CPU.

Bit 4: IT3, Interrupt 3 type control bit.

- 0: Cleared by CPU to specify low level triggered on Interrupt 3. If AUXR.INT3H is set, this bit specifies high level triggered on /INT3.

- 1: Set by CPU to specify falling edge triggered on Interrupt 3. If AUXR.INT3H is set, this bit specifies rising edge triggered on /INT3.

Bit 3: PX2, External interrupt 2 priority-L register.

- 0: Lower priority, setting with PX2H to select priority level.

- 1: Higher priority, setting with PX2H to select priority level.

Bit 2: EX2, external interrupt 2 enable register.

- 0: Disable external interrupt 2.

- 1: Enable external interrupt 2. This function will be masked when IE.EAC is enabled.

Bit 1: IE2, Interrupt 2 Edge flag.

- 0: Cleared when interrupt start to be serviced. It also could be cleared by CPU.

- 1: Set by hardware when external interrupt edge detected. It also could be set by CPU.

Bit 0: IT2, Interrupt 2 type control bit.

- 0: Cleared by CPU to specify low level triggered on /INT2. If AUXR.INT2H is set, this bit specifies high level triggered on /INT2.

- 1: Set by CPU to specify falling edge triggered on /INT2. If AUXR.INT2H is set, this bit specifies rising edge triggered on /INT2.

#### IPL: Interrupt Priority Low Register

Address=B8H, read/write, Power On + RESET=X0X0-0000

| 7 | 6   | 5 | 4  | 3   | 2   | 1   | 0   |

|---|-----|---|----|-----|-----|-----|-----|

| - | PAC |   | PS | PT1 | PX1 | PT0 | PX0 |

Bit 7: reserved.

Bit 6: PAC, Analog Comparator interrupt priority-L register.

Bit 5: Reserved.

Bit 4: PS, Serial port interrupt priority-L register.

Bit 3: PT1, Timer 1 interrupt priority-L register.

Bit 2: PX1, external interrupt 1 priority-L register.

Bit 1: PT0, Timer 0 interrupt priority-L register.

Bit 2: PX0, external interrupt 0 priority-L register.

#### IPH: Interrupt Priority High Register

Address=B7H, read/write, Power On + RESET=00X0-0000

| 7         | 6         | 5 | 4   | 3    | 2    | 1    | 0    |

|-----------|-----------|---|-----|------|------|------|------|

| PX3H/PTCH | PX2H/PACH |   | PSH | PT1H | PX1H | PT0H | PX0H |

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 20/56

- Bit 7: PX3H/PTCH, external interrupt 3 priority-H register. It has an alternate function for PWM-Timer interrupt priority-H register when CMOD.ECF is enabled.

- Bit 6: PX2H/PACH, external interrupt 2 priority-H register. It has an alternate function for Analog Comparator interrupt priority-H register when IE.EAC is enabled.

- Bit 5: Reserved.

- Bit 4: PSH, Serial port interrupt priority-H register.

- Bit 3: PT1H, Timer 1 interrupt priority-H register.

- Bit 2: PX1H, external interrupt 1 priority-H register.

- Bit 1: PT0H, Timer 0 interrupt priority-H register.

- Bit 2: PX0H, external interrupt 0 priority-H register.

IPL (or XICON) and IPH are combined to form 4-level priority interrupt as the following table.

| {IPH.x , IPL.x} | Priority Level |

|-----------------|----------------|

| 11              | 1 (highest)    |

| 10              | 2              |

| 01              | 3              |

| 00              | 4              |

There are seven interrupt sources available in MG87FE/L2051/4051/6051. Each interrupt source can be individually enabled or disabled by setting or clearing a bit in the SFR named IE. This register also contains a global disable bit(EA), which can be cleared to disable all interrupts at once.

Each interrupt source has two corresponding bits to represent its priority. One is located in SFR named IPH and the other in IPL (or XICON) register. Higher-priority interrupt will be not interrupted by lower-priority interrupt request. If two interrupt requests of different priority levels are received simultaneously, the request of higher priority is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determine which request is serviced. The following table shows the internal polling sequence in the same priority level and the interrupt vector address.

| Source                             | Vector address | Priority within level |

|------------------------------------|----------------|-----------------------|

| External interrupt 0               | 03H            | 1 (highest)           |

| Timer 0                            | 0BH            | 2                     |

| External interrupt 1               | 13H            | 3                     |

| Timer1                             | 1BH            | 4                     |

| Serial Port                        | 23H            | 5                     |

| -                                  | 2BH            | -                     |

| External interrupt 2 or Comparator | 33H            | 6                     |

| External interrupt 3 or PWM-Timer  | 3BH            | 7                     |

The external interrupt /INT0, /INT1, /INT2 and /INT3 can each be either level-activated or transition-activated, depending on bits IT0 and IT1 in register TCON, IT2 and IT3 in register XICON. The flags that actually generate these interrupts are bits IE0 and IE1 in TCON, IE2 and IE3 in XICON. When an external interrupt is generated, the flag that generated it is cleared by the hardware when the service routine is vectored to *only if the interrupt was transition –activated*, then the external requesting source is what controls the request flag, rather than the on-chip hardware.

The Timer0 and Timer1 interrupts are generated by TF0 and TF1, which are set by a rollover in their respective Timer/Counter registers in most cases. When a timer interrupt is generated, the flag that generated it is cleared by the on-chip hardware when the service routine is vectored to.

The serial port interrupt is generated by the logical OR of RI and TI. Neither of these flags is cleared by hardware

when the service routine is vectored to. The service routine should poll RI and TI to determine which one to request service and it will be cleared by software.

/INT2 and Analog Comparator share the same interrupt vector, 33H. If IE.EAC is enabled, the interrupt vector, 33H will be used for Analog Comparator with the interrupt flag, ACSR.ACF, and IE2 will not be cleared when 33H interrupt vector is addressed to.

If IE.EAC is disabled, the interrupt vector, 33H, will be used for /INT2 and the interrupt flag, XICON.IE2, that will be cleared when EX2 is enabled and the interrupt vector is addressed to.

/INT3 and PWM-Timer share the same interrupt vector, 3BH. If CMOD.ECF is enabled, the interrupt vector, 3BH will be used for PWM-Timer with the interrupt flag, CCON.CF, and IE3 will not be cleared when 3BH interrupt vector is addressed to.

If CMOD.ECF is disabled, the interrupt vector, 3BH, will be used for /INT3 and the interrupt flag, XICON.IE3, that will be cleared when EX3 is enabled and the interrupt vector is addressed to.

All of the bits that generate interrupts can be set or cleared by software, with the same result as though it had been set or cleared by hardware. In other words, interrupts can be generated or pending interrupts can be canceled in software.

#### How hardware see the interrupts

Each interrupt flag is sampled at S5P2 of every machine cycle. The samples are polled during the next S5P2. If one of the flags was in a set condition at S5P2 of the first cycle, the second cycle(polling cycle) will find it and the interrupt system will generate an hardware LCALL to the appropriate service routine as long as it is not blocked by any of the following conditions.

Block conditions:

- An interrupt of equal or higher priority level is already in progress.

- The current cycle (polling cycle) is not the final cycle in the execution of the instruction in progress.

- The instruction in progress is RETI or any write to the IE, IP or IPH registers.

Any of these three conditions will block the generation of the hardware LCALL to the interrupt service routine. Condition 2 ensures that the instruction in progress will be completed before vectoring into any service routine. Condition 3 ensures that if the instruction in progress is RETI or any access to IE or IP, then at least one or more instruction will be executed before any interrupt is vectored to.

The polling cycle is repeated with each machine cycle, and the values polled are the values that were present at S5P2 of the previous machine cycle. Note that if an interrupt flag is active but not being responded to for one of the above conditions, if the flag is not still active when the blocking condition is removed, the denied interrupt will not be serviced. In other words, the interrupt flag was once active but not being responded to for one of the above conditions, if the flag is not still active when the blocking condition is removed, the denied interrupt will not be serviced. The flag is not still active when the blocking condition is removed, the denied interrupt will not be serviced. The interrupt flag was once active but not serviced is not kept in memory. Each polling cycle is new.

# 10. Timers/Counters

MG87FE/L2051/4051/6051 has two Timers/Counters: Timer 0 and Timer 1. All of them can be configured as timers or event counters.

In the "timer" function, the register is incremented every machine cycle. In other words, it is to count the machine cycle. Due to 12(6) oscillator periods in a machine cycle, the count rate is 1/12(1/6) of the oscillator frequency.

In the "counter" function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0 or T1. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected.

## 10.1. Timer0 and Timer1

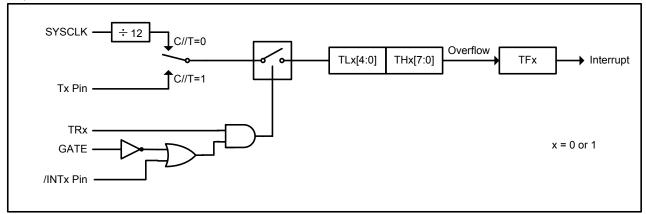

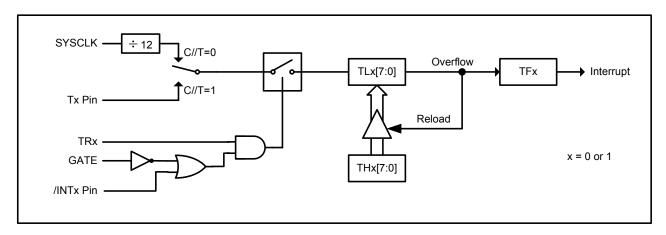

### 10.1.1. Mode 0 Structure

The timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the timer interrupt flag TFx. The counted input is enabled to the timer when TRx = 1 and either GATE=0 or INTx = 1. Mode 0 operation is the same for Timer0 and Timer1.

### 10.1.2. Mode 1 Structure

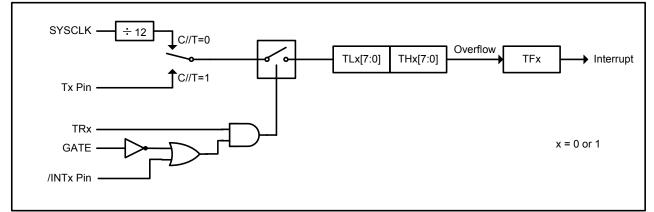

Mode1 is the same as Mode0, except that the timer register is being run with all 16 bits.

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D 23/56

### 10.1.3. Mode 2 Structure

Mode 2 configures the timer register as an 8-bit counter(TLx) with automatic reload. Overflow from TLx not only set TFx, but also reload TLx with the content of THx, which is determined by software. The reload leaves THx unchanged. Mode 2 operation is the same for Timer0 and Timer1.

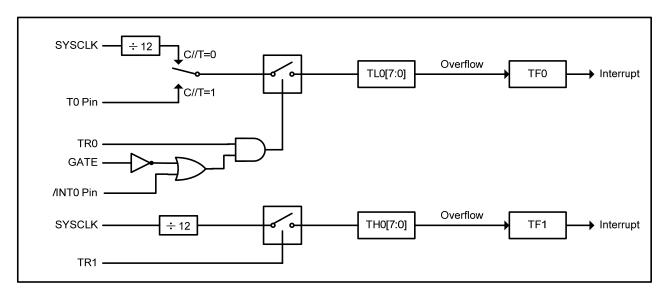

### 10.1.4. Mode 3 Structure

Timer1 in Mode3 simply holds its count, the effect is the same as setting TR1 = 1. Timer0 in Mode 3 enables TL0 and TH0 as two separate 8-bit counters. TL0 uses the Timer0 control bits such like C/T, GATE, TR0, INT0 and TF0. TH0 is locked into a timer function (can not be external event counter) and take over the use of TR1, TF1 from Timer1. TH0 now controls the Timer1 interrupt.

This document information is the intellectual property of Megawin Technology. © Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D 24/56

### 10.1.5. Timer0/1 Register

#### TMOD: Timer/Counter Mode Control Register

Address=89H, read/write, Power On + RESET=0000-0000

|                  | .,  | ,  |    |      |     |    |    |

|------------------|-----|----|----|------|-----|----|----|

| 7                | 6   | 5  | 4  | 3    | 2   | 1  | 0  |

| GATE             | C/T | M1 | MO | GATE | C/T | M1 | M0 |

| ←Timer1→ ←Timer0 |     |    |    |      |     |    |    |

Bit 7/3: Gate, Gating control for Timer1/0.

0: Disable gating control for Timer1/0.

1: Enable gating control for Timer1/0. When set, Timer1/0 or Counter1/0 is enabled only when /INT1 or /INT0 pin is high and TR1 or TR0 control bit is set.

Bit 6/2: C/T, Timer for Counter function selector.

- 0: Clear for Timer operation, input from internal system clock.

- 1: Set for Counter operation, input form T1 input pin.

Bit 5~4/1~0: Operating mode selection.

| M1 | MO         | Operating Mode                                                  |

|----|------------|-----------------------------------------------------------------|

| 0  | 0          | 13-bit timer/counter for Timer0 and Timer1                      |

| 0  | 1          | 16-bit timer/counter for Timer0 and Timer1                      |

| 1  | 0          | 8-bit timer/counter with automatic reload for Timer0 and Timer1 |

| 1  | 1 (Timer0) | TL0 is 8-bit timer/counter, TH0 is locked into 8-bit timer      |

| 1  | 1 (Timer1) | Timer/Counter1 Stopped                                          |

#### TCON: Timer/Counter Control Register

Address=88H, read/write, Power On + RESET=0000-0000

|     |     | ,   |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

Bit 7: TF1, Timer 1 overflow flag.

0: Cleared by hardware when the processor vectors to the interrupt routine, or cleared by software.

1: Set by hardware on Timer/Counter 1 overflow, or set by software.

Bit 6: TR1, Timer 1 Run control bit.

0: Cleared by software to turn Timer/Counter 1 off.

1: Set by software to turn Timer/Counter 1 on.

Bit 5: TF0, Timer 0 overflow flag.

0: Cleared by hardware when the processor vectors to the interrupt routine, or cleared by software.

1: Set by hardware on Timer/Counter 0 overflow, or set by software.

Bit 4: TR0, Timer 0 Run control bit.

- 0: Cleared by software to turn Timer/Counter 0 off.

- 1: Set by software to turn Timer/Counter 0 on.

Bit 3: IE1, Interrupt 1 Edge flag.

0: Cleared when interrupt processed on if transition-activated.

1: Set by hardware when external interrupt 1 edge is detected (transmitted or level-activated).

Bit 2: IT1: Interrupt 1 Type control bit.

0: Cleared by software to specify low level triggered external interrupt 1.

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D

25/56

1: Set by software to specify falling edge triggered external interrupt 1.

Bit 1: IE0, Interrupt 0 Edge flag.

- 0: Cleared when interrupt processed on if transition-activated.

- 1: Set by hardware when external interrupt 0 edge is detected (transmitted or level-activated).

Bit 0: IT0: Interrupt 0 Type control bit.

- 0: Cleared by software to specify low level triggered external interrupt 0.

- 1: Set by software to specify falling edge triggered external interrupt 0.

MG87FE/L2051/4051/6051

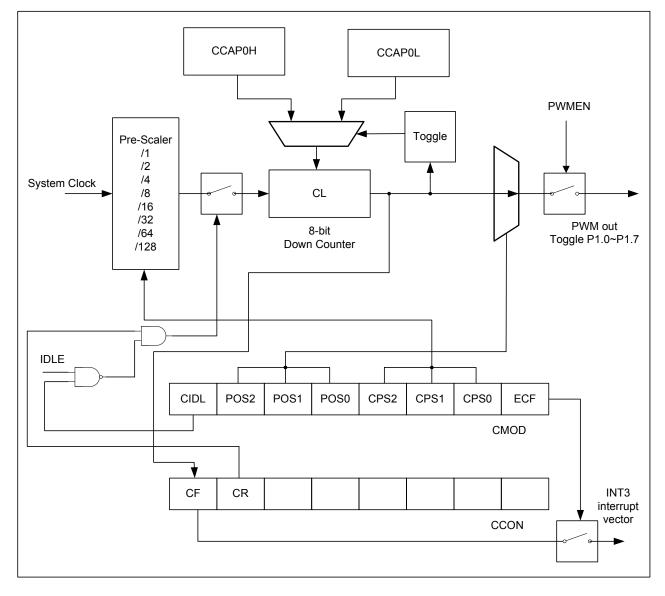

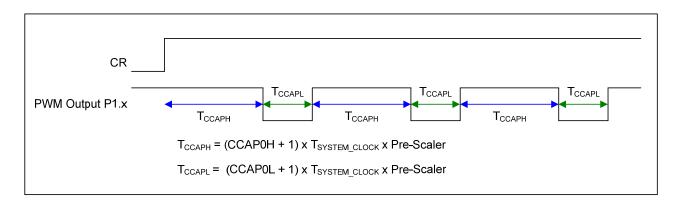

### 10.2. PWM-Timer

An 8-bits timer that special designed for PWM generator.

### 10.2.1. PWM-Timer Structure

This document information is the intellectual property of Megawin Technology. © Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D 27/56

Preliminary, v 1.03

### 10.2.2. PWM-Timer Register

#### CMOD: PWM-timer Mode Register

Address=D9H, read/write, Power On + RESET=0000-0000

|      |      | ,    |      |      |      |      |     |

|------|------|------|------|------|------|------|-----|

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0   |

| CIDL | POS2 | POS1 | POS0 | CPS2 | CPS1 | CPS0 | ECF |

Bit 7: CIDL, Counter Idle Control.

0: Program the PWM-Timer to continue functioning during IDLE mode.

1: Program the PWM-Timer to be gated off during IDLE mode.

Bit 6~4: POS[2:0], PWM output port select.

| POS[2:0] | PWMEN | PWM Output Port |

|----------|-------|-----------------|

| 0 0 0    | 1     | P1.0            |

| 0 0 1    | 1     | P1.1            |

| 0 1 0    | 1     | P1.2            |

| 0 1 1    | 1     | P1.3            |

| 1 0 0    | 1     | P1.4            |

| 1 0 1    | 1     | P1.5            |

| 1 1 0    | 1     | P1.6            |

| 1 1 1    | 1     | P1.7            |

| XXX      | 0     | Disabled        |

Bit 3~1: CPS[2:0], Counter Pre-scalar Select.

| CPS[2:0] | Pre-scalar |

|----------|------------|

| 0 0 0    | 1          |

| 0 0 1    | 2          |

| 0 1 0    | 4          |

| 0 1 1    | 8          |

| 1 0 0    | 16         |

| 1 0 1    | 32         |

| 1 1 0    | 64         |

| 1 1 1    | 128        |

Bit 0: ECF, Enable PWM-Timer underflow interrupt.

0: Disables CF bit in CCON to generate an interrupt.

1: Enables CF bit in CCON to generate an interrupt.

This document information is the intellectual property of Megawin Technology. © Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D 28/56

Preliminary Ver 1.00

#### CCON: PWM-timer Control Register

Address=D8H, read/write, Power On + RESET=00XX-XXXX

| 7  | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|---|---|---|---|---|---|

| CF | CR | - | - | - | - | - | - |

Bit 7: CF, PWM-timer underflow Flag.

0: This flag can only be cleared by software.

1: Set by hardware when the counter rolls under. CF flags an interrupt if bit ECF in CMOD is set. CF may be set by either hardware or software.

Bit 6: CR, PWM-timer Run control bit.

0: Must be cleared by software to turn the PWM-Timer counter off.

1: Set by software to turn the PWM-Timer counter on.

Bit 5~0: Reserved.

#### CACP0L: PWM-Timer L-Duty Register

Address=EAH, read/write, Power On + RESET=0000-0000

|   |   | , |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| - | - | - | - | - | - | - | - |

#### CACP0H: PWM-Timer H-Duty Register

Address=FAH, read/write, Power On + RESET=0000-0000

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

# 11. UART

The serial port(UART) of MG87FE/L2051/4051/6051 support full-duplex transmission. It can transmit and receive simultaneously. The serial port receive and transmit share the same SFR – SBUF, but actually there is two SBUFs in the chip, one is for transmit and the other is for receive. The serial port can be operated in 4 different modes.

## 11.1. UART Structure

#### Mode 0

Serial data enters and exits through RXD(P3.0) and TXD(P3.1) outputs the shift clock. 8-bits are transmitted/received with LSB first. The baud rate is fixed at 1/12 the system clock frequency.

| Baud Rate in Mode 0 = - | F <sub>SYSCLK</sub> |  |

|-------------------------|---------------------|--|

|                         | 12                  |  |

#### Mode1

10 bits are transmitted through TXD or received through RXD. The frame data includes a start bit(0), 8 data bits and a stop bit(1). One receive, the stop bit goes into RB8 in SFR – SCON. The baud rate is variable.

Baud Rate in Mode 1 =  $\frac{2^{\text{SMOD}}}{32}$  X (timer1 overflow rate)

#### Mode2

11 bits are transmitted through TXD or received through RXD. The frame data includes a start bit(0), 8 data bits, a programmable 9th bit and a stop bit(1). On transmit, the 9th data bit comes from TB8 in SCON. On receive, the 9th data bit goes into RB8 in SCON. The baud rate is programmable to either 1/32 or 1/64 the system clock frequency.

Baud Rate in Mode 2 =  $\frac{2^{\text{SMOD}}}{64}$  X F<sub>SYSCLK</sub>

#### Mode3

Mode 3 is the same as mode 2 except the baud rate is variable.

Baud Rate in Mode 3 =

$$\frac{2^{\text{SMOD}}}{32}$$

X (timer1 overflow rate)

In all four modes, transmission is initiated by any instruction that use SBUF as a destination register. Reception is initiated in mode 0 by the condition RI = 0 and REN = 1. Reception is initiated in the other modes by the incoming start bit with 1-to-0 transition if REN=1.

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 30/56

MG87FE/L2051/4051/6051

Preliminary Ver 1.00

#### Automatic Address Recognition

Automatic Address Recognition is a feature which allows the UART to recognize certain addresses in the serial bit stream by using hardware comparison circuit. This feature improves the overhead of software by eliminating the need in examine every incoming address. This feature is enabled by setting the SM2 bit in SCON. In mode2 and mode3, the receive interrupt flag(RI) will be automatically set when the received byte contains either the "Given" address or the "Broadcast" address. These two modes require the 9<sup>th</sup> received bit is a 1 to indicate that received information is an address and not the data byte.

In mode1, the RI flag will be set if SM2 is enabled and a valid stop bit is received which the stop bit follows the 8 address bits and the information is either a given or Broadcast address.

In mode 0, SM2 is ignored.

#### Framing Error Detection

Framing Error Detection allows the serial port to check for valid stop bits in modes 1, 2, or3. A missing stop bit can be caused, for example, by noise on the serial lines, or transmission by two CPUs simultaneously.

If a stop bit is missing, a Framing Error bit FE is set. The FE bit can be checked in software after each reception to detect communication errors. Once set, the FE bit must be cleared in software. A valid stop bit will not clear FE.

The FE bit is located in SCON and shares the same bit address as SM0. Control bit SMOD0 in the PCON register (location PCON.6) determines whether the SM0 or FE bit is accessed. If SMOD0 = 0, then accesses to SCON.7 are to SM0. IF SMOD0 = 1, then accesses to SCON.7 are to FE.

### 11.2. UART Register

#### SCON: Serial port Control Register

Address=98H, read/write, Power On + RESET=0000-0000

| 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|--------|-----|-----|-----|-----|-----|----|----|

| SM0/FE | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

Bit 7: FE, Framing Error bit. The SMOD0 bit must be set to enable access to the FE bit.

0: The FE bit is not cleared by valid frames but should be cleared by software.

1: This bit is set by the receiver when an invalid stop bit is detected.

Bit 7: Serial port mode bit 0, (SMOD0 must = 0 to access bit SM0) Bit 6: Serial port mode bit 1.

| SM0 | SM1 | Mode | Description    | Baud Rate                            |

|-----|-----|------|----------------|--------------------------------------|

| 0   | 0   | 0    | shift register | F <sub>SYSCLK</sub> /12              |

| 0   | 1   | 1    | 8-bit UART     | variable                             |

| 1   | 0   | 2    | 9-bit UART     | $F_{SYSCLK}$ /64 or $F_{SYSCLK}$ /32 |

| 1   | 1   | 3    | 9-bit UART     | variable                             |

Bit 5: Serial port mode bit 2.

0: Disable SM2 function.

1: Enable the automatic address recognition feature in Modes 2 and 3. If SM2=1, RI will not be set unless the received 9th data bit is 1, indicating an address, and the received byte is a Given or Broadcast address. In

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D 31/56

mode1, if SM2=1 then RI will not be set unless a valid stop Bit was received, and the received byte is a Given or Broadcast address. In Mode 0, SM2 should be 0.

Bit 4: REN, Enable serial reception.

- 0: Clear by software to disable reception.

- 1: Set by software to enable reception.

Bit 3: TB8, The 9<sup>th</sup> data bit that will be transmitted in Modes 2 and 3. Set or clear by software as desired.

Bit 2: RB8, In Modes 2 and 3, the 9<sup>th</sup> data bit that was received. In Mode 1, if SM2 = 0, RB8 is the stop bit that was received. In Mode 0, RB8 is not used.

Bit 1: TI. Transmit interrupt flag.

0: Must be cleared by software.

1: Set by hardware at the end of the 8<sup>th</sup> bit time in Mode 0, or at the beginning of the stop bit in the other modes, in any serial transmission.

Bit 0: RI. Receive interrupt flag.

- 0: Must be cleared by software.

- 1: Set by hardware at the end of the 8<sup>th</sup> bit time in Mode 0, or halfway through the stop bit time in the other modes, in any serial reception (except see SM2).

#### SBUF: Serial Buffer Register

Address=99H, read/write, Power On + RESET=XXXX-XXXX

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Bit 7~0: It is used as the buffer register in transmission and reception.

#### SADDR: Slave Address Register

|                                                     | a / 0 / la a / 000 |   |   |   |   |   |   |  |  |  |  |

|-----------------------------------------------------|--------------------|---|---|---|---|---|---|--|--|--|--|

| Address=A9H, read/write, Power On + RESET=0000-0000 |                    |   |   |   |   |   |   |  |  |  |  |

| 7                                                   | 6                  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|                                                     |                    |   |   |   |   |   |   |  |  |  |  |

#### SCON: Slave Address Mask Register

| Address=B9H, read/write, Power On + RESET=0000-0000 |   |   |   |   |   |   |   |

|-----------------------------------------------------|---|---|---|---|---|---|---|

| 7                                                   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|                                                     |   |   |   |   |   |   |   |

SADDR register is combined with SADEN register to form Given/Broadcast Address for automatic address recognition. In fact, SADEN functions as the "mask" register for SADDR register. The following is the example for it.

| SADDR | = | 1100 0000 |  |

|-------|---|-----------|--|

| SADEN | = | 1111 1101 |  |

| Given | = | 1100 00x0 |  |

The Given slave address will be checked except bit 1 is treated as "don't care"

The Broadcast Address for each slave is created by taking the logical OR of SADDR and SADEN. Zero in this result is considered as "don't care". Upon reset, SADDR and SADEN are loaded with all 0s. This produces a Given Address of all "don't care" and a Broadcast Address of all "don't care". This disables the automatic address detection feature.

This document information is the intellectual property of Megawin Technology. © Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D 32/56

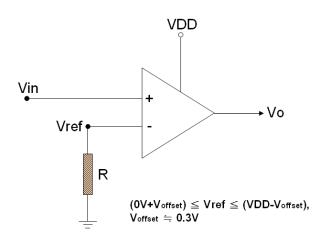

# 12. Analog Comparator

A single analog comparator is provided in the MG87FE/L2051/4051/6051. The comparator operation is such that the output is a logical "HIGH" when the positive input AIN0 (P1.0]) is greater than the negative input AIN1 (P1.1). Otherwise the output is "LOW". Setting the ACEN bit in ACSR enables the comparator. When the comparator is first enabled, the comparator output and interrupt flag are not guaranteed to be stable for 10 microseconds. The corresponding comparator interrupt should not be enabled during that time, and the comparator interrupt flag must be cleared before the interrupt is enabled in order to prevent an immediate interrupt service.

The comparator may be configured to cause an interrupt under a variety of output value conditions by setting the ACM bits in ACSR. The comparator interrupt flag ACF in ACSR is set whenever the comparator output matches the condition specified by ACM. The flag may be polled by firmware or may be used to generate an interrupt and must be cleared by firmware. The analog comparator is always disabled during Idle or Power-down modes.

# P1.0 (AIN0) P1.1 (AIN1) Timer 1 Overflow CF Start Compare Start Compare Compare of negative edge comparator interrupt with debounce

# 12.1. Analog Comparator Structure

The comparator output is sampled at every State 4 (S4) of every machine cycle. The conditions on the analog inputs may be such that the comparator output will toggle excessively. This is especially true if applying slow moving analog inputs. Three de-bouncing modes are provided to filter out this noise. In de-bouncing mode, the comparator uses Timer-1 to modulate its sampling time. When a relevant transition occurs, the comparator waits until two Timer-1 overflows have occurred before re-sampling the output. If the new sample agrees with the expected value, ACF is set. Otherwise, the event is ignored. The filter may be tuned by adjusting the timeout period of Timer-1. Because Timer-1 is free running, the de-bouncer must wait for two overflows to guarantee that the sampling delay is at least 1 timeout period. Therefore, after the initial edge event, the interrupt may occur between 1 and 2 timeout periods later.

# 12.2. Analog Comparator Register

#### ACSR: Analog Comparator Control & Status Register

| Address=97H, read/write, Power On + RESET=0xx0-0000 |   |   |     |      |      |      |      |

|-----------------------------------------------------|---|---|-----|------|------|------|------|

| 7                                                   | 6 | 5 | 4   | 3    | 2    | 1    | 0    |

| ACIDX                                               | - | - | ACF | ACEN | ACM2 | ACM1 | ACM0 |

Bit 7: ACIDX, Analog Comparator IDLE control.

0: Program the Analog Comparator to be gated off during IDLE mode.

1: Program the Analog Comparator to continue functioning during IDLE mode.

Bit 6~5: Reserved.

Bit 4: ACF. Analog Comparator Interrupt Flag.

- 0: The flag must be cleared by software.

- 1: Set when the comparator output meets the conditions specified by the ACM [2:0] bits and ACEN is set. The interrupt may be enabled/disabled by setting/clearing bit 6 of IE.

Bit 3: ACEN. Analog Comparator Enable.

- 0: Clearing this bit will force the comparator output low and prevent further events from setting ACF.

- 1: Set this bit to enable the comparator.

Bit 2~0: ACM2 ~ ACM1, Analog Comparator Interrupt Mode.

| ACM[2:0] | Interrupt Mode               |  |  |  |

|----------|------------------------------|--|--|--|

| 0 0 0    | Negative (Low) level         |  |  |  |

| 0 0 1    | Positive edge                |  |  |  |

| 0 1 0    | Toggle with de-bounce        |  |  |  |

| 0 1 1    | Positive edge with de-bounce |  |  |  |

| 1 0 0    | Negative edge                |  |  |  |

| 1 0 1    | Toggle                       |  |  |  |

| 1 1 0    | Negative edge with de-bounce |  |  |  |

| 1 1 1    | Positive (High) level        |  |  |  |

This document information is the intellectual property of Megawin Technology. © Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D 34/56

MG87FE/L2051/4051/6051

Preliminary Ver 1.00

# 13. Watch Dog Timer (WDT)

### 13.1. WDT Structure

# 13.2. WDT Register

#### WDTCR: Watch-Dog-Timer Control Register

Address=E1H. read/write. Power On + Reset =0x00-0000

| 7   | 6 | 5   | 4    | 3    | 2   | 1   | 0   |

|-----|---|-----|------|------|-----|-----|-----|

| WRF | - | ENW | CLRW | WIDL | PS2 | PS1 | PS0 |

Bit 7: WRF, WDT reset flag.

0: This bit should be cleared by software.

1: When WDT overflows, this bit is set by hardware.

Bit 6: Reserved.

Bit 5: ENW. Enable WDT.

0: ENW can not be cleared by software.

1: Enable WDT while it is set.

Bit 4: CLRW. Clear WDT counter.

0: Hardware will automatically clear this bit.

1: Clear WDT to recount while it is set.

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D

35/56

Bit 3: WIDL. WDT idle control.

0: WDT stops counting while the MCU is in idle mode.

1: WDT keeps counting while the MCU is in idle mode.

Bit 2~0: PS2 ~ PS0, select pre-scalar output for WDT time base input.

| PS[2:0] | Pre-scalar Value |  |  |

|---------|------------------|--|--|

| 0 0 0   | 2                |  |  |

| 0 0 1   | 4                |  |  |

| 0 1 0   | 8                |  |  |

| 0 1 1   | 16               |  |  |

| 1 0 0   | 32               |  |  |

| 1 0 1   | 64               |  |  |

| 1 1 0   | 128              |  |  |

| 1 1 1   | 256              |  |  |

Preliminary Ver 1.00

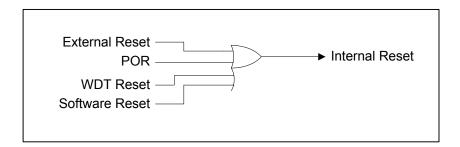

# 14. Reset

During reset, all I/O Registers are set to their initial values, the port pins are weakly pulled to VDD, and the program starts execution from the Reset Vector, 0000H, or ISP start address by OR setting. MG87FE/L2051/4051/6051 all have four sources of reset: external reset, power-on reset, WDT reset, and software reset.

### 14.1. Reset Source

# 15. Power Management

MG87FE/L2051/4051/6051 supports two power-reducing modes: Idle and Power-down mode. These two modes are accessed through the PCON register.

### 15.1. Power Saving Mode

### 15.1.1. Idle Mode

Setting the IDL bit in PCON enters idle mode. Idle mode halts the internal CPU clock. The CPU state is preserved in its entirety, including the RAM, stack pointer, program counter, program status word, and accumulator. The Port pins hold the logical states they had at the time that Idle was activated. Idle mode leaves the peripherals running in order to allow them to wake up the CPU when an interrupt is generated. Timer 0, Timer 1, PWM-Timer and the UART will continue to function during Idle-mode. The analog comparator is disabled during Idle. Any enabled interrupt source or reset may terminate Idle-mode. When exiting Idle-mode with an interrupt, the interrupt will immediately be serviced, and following RETI, the next instruction to be executed will be the one following the instruction that put the device into Idle.

P1.0 and P1.1 should be set to "0" if no external pull-ups are used, or set to "1" if external pull-ups are used, or set to "1" if AUXR.P10PU&P11PU are enabled.

### 15.1.2. Power-down Mode

Setting the PD bit in PCON enters Power-down mode. Power-down mode stops the oscillator and powers down the Flash memory in order to minimize power consumption. Only the power-on circuitry will continue to draw power during Power-down. During Power-down the power supply voltage may be reduced to the RAM keep-alive voltage. The RAM contents will be retained; however, the SFR contents are not guaranteed once VDD has been reduced. Power-down may be exited by external reset, power-on reset, enabled external interrupts, or enabled wake-up GPIOs.

The user should not attempt to enter (or re-enter) the power-down mode for a minimum of 4 µs until after one of the following conditions has occurred: Start of code execution (after any type of reset), or exit from power-down mode.

### 15.1.3. Interrupt Recovery from Power-down

Four external interrupts may be configured to terminate Power-down mode. External interrupts /INT0 (P3.2), /INT1 (P3.3), /INT2 (P4.3) and /INT2 (P4.2) may be used to exit Power-down. To wake up by external interrupt /INT0, /INT1, /INT2, or /INT3, the interrupt must be enabled and configured for level-sensitive operation.

If the interrupt vector of /INT2 (P4.3) is occupied by Analog Comparator, low level P4.3 input still have wake-up capability when /INT2 interrupt enable, XICON.EX2, is set (enabled). If the interrupt vector of /INT3 (P4.2) is occupied by PWM-Timer underflow, low level P4.2 input still have wake-up capability when /INT3 interrupt enable, XICON.EX3, is set (enabled).

When terminating Power-down by an interrupt, two different wake-up modes are available. When PWDEX in CKCON3.2 is zero, the wake up period is internally timed. At the falling edge on the interrupt pin, Power-down is

This document information is the intellectual property of Megawin Technology. © Megawin Technology Co., Ltd. 2009 All rights reserved. QP-7300-03D 38/56

Preliminary Ver 1.00

exited, the oscillator is restarted, and an internal timer begins counting. The internal clock will not be allowed to propagate and the CPU will not resume execution until after the timer has reached internal counter full. After the timeout period, the interrupt service routine will begin. To prevent the interrupt from re-triggering, the ISR should disable the interrupt before returning. The interrupt pin should be held low until the device has timed out and begun executing.